# An Investigation of Electrical and Dielectric Parameters of Sol–Gel Process Enabled $\beta$ -Ga<sub>2</sub>O<sub>3</sub> as a Gate Dielectric Material

Ahmet Kaya, Howard Mao, Jianyi Gao, Rajesh V. Chopdekar, Member, IEEE, Yayoi Takamura, Srabanti Chowdhury, Member, IEEE, and M. Saif Islam, Member, IEEE

Abstract—In this paper,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films were grown on a p-Si substrate using the sol-gel method. Structural characterization of the films was performed using X-ray diffraction. Electrical parameters such as breakdown field, interface traps density (D<sub>it</sub>), and series resistance  $(R_s)$  were investigated at room temperature. The interface trap density was found to be  $10^{12} \text{ eV}^{-1} \text{ cm}^{-2}$  using the Hill-Coleman method. This result is valuable for MOS capacitor applications. Dielectric parameters were investigated in the wide frequency range (20 kHz-1 MHz) at room temperature. We observed that these parameters have a strong dependence on frequency and voltage.

Index Terms— $\beta$ -Ga<sub>2</sub>O<sub>3</sub> dielectric film, dielectric properties, electrical properties.

#### I. INTRODUCTION

N RECENT years, there has been a strong demand for high- $\mathbf{I}$  k gate dielectrics able to provide an increased gate capacitance at small thickness. Gate oxides are no longer restricted to the silicon dioxide commonly used in the past. Materials such as aluminum oxide  $(Al_2O_3)$  [1], zirconium oxide  $(ZrO_2)$ [2], hafnium oxide (HfO<sub>2</sub>) [3], aluminum nitride (AlN) [4], and gadolinium oxide  $(Gd_2O_3)$  [5] have all been used as gate dielectrics for semiconductor devices. The gate dielectric is an important part of a MOS capacitor because of its effect on the gate capacitance. In order to achieve a high gate capacitance, a material with a high dielectric constant should be used. For this reason, Ga<sub>2</sub>O<sub>3</sub> thin films with a dielectric constant of between 9.93 and 10.2 [6] are a promising dielectric material. This is far greater than silicon dioxide, which has a dielectric constant of only 3.9 [7]. Due to its higher dielectric constant, Ga<sub>2</sub>O<sub>3</sub> thin films are more resistant to tunneling of carriers through the gate of the capacitor.  $Ga_2O_3$  also has a wide bandgap (~4.9 eV) and high chemical and thermal stability.

Manuscript received December 20, 2016; revised February 17, 2017; accepted February 22, 2017. Date of publication March 21, 2017; date of current version April 19, 2017. The work was supported by the Army Research Office Research under Grant W911NF-14-1-0341. The review of this paper was arranged by Editor Anisul Haque.

A. Kaya, H. Mao, J. Gao, S. Chowdhury, and M. S. Islam are with the Department of Electrical and Computer Engineering, University of California, Davis, CA 95616 USA (e-mail: sislam@ucdavis.edu).

R. V. Chopdekar and Y. Takamura are with the Department of Materials Science and Engineering, University of California, Davis, CA 95616 USA. Color versions of one or more of the figures in this paper are available

online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2017.2675990

Shih et al. [8] used Ga<sub>2</sub>O<sub>3</sub> films as both a gate dielectric for an AlGaN/GaN MOS high-electron-mobility transistors (HEMT) and as a passivation layer for a gate-stack and found that the leakage current was reduced by two orders of magnitude. Jevasuwan et al. [9] grew a monolayer of Ga<sub>2</sub>O<sub>3</sub> on InGaAs and inserted it into an Al<sub>2</sub>O<sub>3</sub>/InGaAs stack, observing that it reduced trap density and reduced the formation of native oxide. Allen et al. [10] showed that Ga<sub>2</sub>O<sub>3</sub> thin films can be used to passivate Si solar cells by reducing trap density and contributing to a high negative charge density. Seok et al. [11] sputtered Ga<sub>2</sub>O<sub>3</sub> onto AlGaN/GaN HEMTs and discovered that it reduced the leakage current and increased the breakdown voltage. Lin et al. [12] used a layer of Ga<sub>2</sub>O<sub>3</sub> in an InGaN light-emitting diode for passivation and to reduce leakage current. A theoretical study also showed that layers of Ga<sub>2</sub>O<sub>3</sub> can be grown on  $\alpha$ -Fe<sub>2</sub>O<sub>3</sub> to passivate surface states that would otherwise trap holes [13]. These examples show that a Ga<sub>2</sub>O<sub>3</sub> film is an excellent dielectric material.

In this paper, the sol-gel method was used to as simple and in expensive method. However, the quality of thin film obtained is not as high as that obtained using other deposition methods. Kumar et al. [14] used the sol-gel method to grow titanium dioxide films of different thicknesses in fabricating MOS capacitors. Amiri et al. [15] prepared a gel electrolyte for a supercapacitor consisting of KCl and potassium poly (acrylate) (PAAK) polymer and used spin coating to create a uniform surface of the gel electrolyte. These examples show that the sol-gel method is a valid way of growing thin films for dielectrics in capacitors. Therefore, we fabricated an MOS capacitor using the sol-gel method to grow Ga<sub>2</sub>O<sub>3</sub> as the gate dielectric and measured its dielectric properties using impedance spectroscopy.

To better understand the effectiveness of sol-gel enabled Ga<sub>2</sub>O<sub>3</sub> as a dielectric, it is important to know the electric and dielectric properties of the grown material. For this purpose, the Hill-Coleman method [16] and impedance spectroscopy was performed on the  $Ga_2O_3$  heterostructure. Impedance spectroscopy is a useful method for revealing internal dynamics of a system across the frequency spectrum. Alifragis et al. [17] used impedance spectroscopy to determine the structure of a GaN gas sensor. Lazarescu et al. [18] found that pH and applied potential had a significant impact on

0018-9383 © 2017 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

the GaAs-cysteine thiolate interface using impedance spectroscopy. Impedance spectroscopy was used to find dielectric parameters of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin film as function of frequency and voltage.

## **II. EXPERIMENTS**

MOS capacitors were fabricated on (100) p-type Si wafers doped with boron. The wafers were 280- $\mu$ m thick and had a resistivity between 0.005 and 0.08  $\Omega$  cm. The Si wafer was cleaned using acetone for 5 min and then in methanol for 5 min in an ultrasonic bath. Following that, the wafer was rinsed with deionized water for 5 min. To grow the Ga<sub>2</sub>O<sub>3</sub> thin film, first gallium nitrate hydrate (Ga(NO<sub>3</sub>)<sub>3</sub> · xH<sub>2</sub>O) powder was dissolved in ethanol (C<sub>2</sub>H<sub>6</sub>O) to form a solution. Then, this solution was drop-cast onto a bare p-Si substrate and spun for 30 s at 3000 rpm in the ambient atmosphere.

Afterward, the film was heated at 100 °C on a hot plate for 30 min to evaporate the ethanol and then annealed in a furnace at 800 °C for 2 h in Ar ambient. In the literature, different annealing temperatures for Ga<sub>2</sub>O<sub>3</sub> have been used to improve film crystallinity. Cheng et al. [19] annealed Ga<sub>2</sub>O<sub>3</sub> films in N<sub>2</sub> and O<sub>2</sub> at 1000 °C for 1 h. This caused grain size to increase significantly and photoluminescence intensity to greatly increase. The absorption edges of the films also shifted to shorter wavelengths. Suzuki et al. [20] annealed Ga<sub>2</sub>O<sub>3</sub> photodiodes in N<sub>2</sub> at temperatures ranging from 100 °C to 500 °C for 10 min. This led to a reduction of the forward turn-on voltage and at 400 °C, the photocurrent and responsivity were dramatically enhanced. Goyal et al. [21] annealed Ga<sub>2</sub>O<sub>3</sub> thin films at 600 °C, 800 °C, and 1000 °C in air for 24 h. At higher temperatures, the surface feature size of the Ga<sub>2</sub>O<sub>3</sub> film increased. Higher annealing temperatures were also correlated with a wider bandgap. Berbenni et al. [22] explain the process through which  $Ga(NO_3)_3 \cdot xH_2O$  thermally decomposes into Ga<sub>2</sub>O<sub>3</sub>.

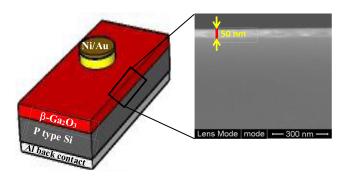

X-ray diffractometer characterization of films after the 800 °C anneal step was performed with a Bruker D8 Discover high-resolution X-ray diffraction system equipped with a Cu K-alpha X-ray source. Measurements were performed in a grazing incidence angle to minimize diffracted intensity from the Si substrate geometry maximizing the intensity from the Ga<sub>2</sub>O<sub>3</sub> film. After structural characterization of the films, electron beam evaporation was used to deposit 20 nm of Ni and 200 nm of Au for contacts through a shadow mask. A Keithley 4200-SCS parameter analyzer was used to measure C-V characteristics using a sweep rate of 100 mV/s, ac amplitude of 30 mV, and a voltage step of 0.1 V at various frequencies. A HP4156B semiconductor parameter analyzer was used to measure the I-V characteristics between 5 and -45 V with a voltage step of 0.5 V. A schematic of the device and a cross-sectional SEM image of the Ga2O3/Si interface are presented in Fig. 1.

## **III. RESULTS AND DISCUSSION**

### A. Structural Properties

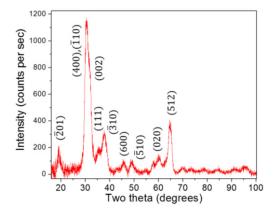

Grazing incidence X-ray diffraction measurements on a  $\sim$ 50-nm Ga<sub>2</sub>O<sub>3</sub> film at an incidence angle of 0.6° are

Fig. 1. Schematic of the device and cross-sectional SEM image of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/Si interface shows the smooth thin film with 50-nm thickness.

Fig. 2. X-ray diffraction pattern of  $Ga_2O_3$  film annealed at 800 °C in Ar ambient, with peak labels corresponding to strong monoclinic  $Ga_2O_3$  reflections.

presented in Fig. 2 over the diffracted angle range of  $2\theta$  = 15-100°. The experimental peak positions and intensities correspond well to a nearly randomly oriented monoclinic  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> phase (JCPDS card 00-041-1103) with peak reflections as indicated. No significant peaks indicative of rhombohedral  $\alpha$ -Ga<sub>2</sub>O<sub>3</sub> (JCPDS card 01-074-1610) or other phases are present in the experimental pattern.

#### **B.** Electrical Properties

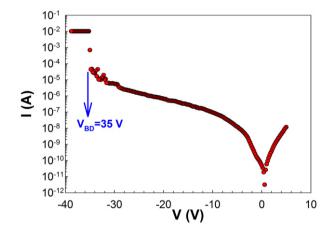

It is well-known that Ga<sub>2</sub>O<sub>3</sub> has a high breakdown field and that therefore it is suitable for high-temperature applications. I-V plots were measured between 5 and -45 V with a voltage step of 0.5 V (Fig. 3). The breakdown field was determined for a 50 nm Ga<sub>2</sub>O<sub>3</sub> thin film which was grown via the solgel method and annealed at 800 °C in Ar ambient. As can be seen from Fig. 3, the breakdown field was calculated to be 7 MV/cm. In the literature, for thermally oxidized Ga<sub>2</sub>O<sub>3</sub> thin films, breakdown fields of 0.65 [23], 1 [24], 3.85 [25], 3.6 [26], and 18 MV/cm [27] have been reported. As seen in Fig. 3, the high leakage current can be attributed to native oxide in between the Ga<sub>2</sub>O<sub>3</sub> and Si interface. The presence of this native oxide reduces the performance of the MOS capacitor by increasing leakage current and the roughness of the surface. The presence of a native oxide also leads to the generation of traps due to stress between the oxide and the silicon substrate [28].

Fig. 3. Reverse bias semilogarithmic I-V curve of the Ni/Au/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/ p-Si MOS capacitor at room temperature. The breakdown field was determined to be 7 MV/cm.

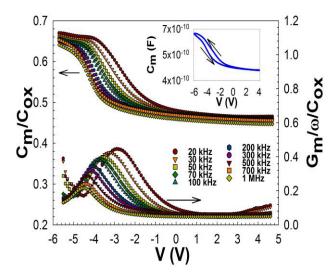

Fig. 4. Measured capacitance ( $C_m$ ) and conductance ( $G_m/\omega$ ) of MOS capacitor ( $C_mG_m$ -V) were normalized by the oxide capacitance ( $C_{ox}$ ) as a function of bias voltage.  $C_mG_m$ -V was measured with a voltage step of 0.1 V and swept between frequencies 20 kHz–1 MHz. The oxide thickness of the Ni/Au/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/P-Si MOS capacitor is 50 nm. Inset: the hysteresis of  $C_m$  versus V with sweeps in two different directions.

The measured capacitance  $(C_m)$  and conductance  $(G_m/W)$  values were normalized by the oxide capacitance  $(C_{ox})$  and are given in Fig. 4. The three regimes of accumulation, depletion, and inversion are shown in the  $C_m/C_{ox}-V$  plot (Fig. 4) and a typical MOS capacitor behavior can be seen. However, the  $C_m/C_{ox}-V$  behavior of the Ni/Au/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/ p-Si MOS capacitor is nonideal. The nonideal MOS capacitor capacitance curve can experience a parallel shift from the ideal curve due to the flat band voltage, fixed charge, oxide trapped charge, interface trapped charge, and mobile oxide charge effects [29], [30].

The  $C_m$ -V curves of the inset of Fig. 4 show that there is an interface layer between the metal and semiconductor. Hysteresis of  $C_m$ -V with two sweep directions, one from the negative voltage to positive voltage and the other positive to negative, can be observed. This behavior can be attributed to mobile charges in an interfacial layer [27], [29]–[31]. Also,

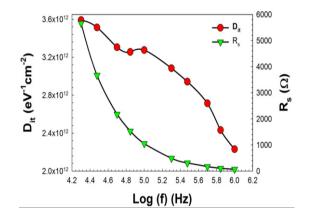

Fig. 5. Variation of interface traps density ( $D_{it}$ ) and series resistance of the MOS capacitor were obtained from  $C_m G_m V$  characteristics in the frequency range of 20 kHz–1 MHz.  $D_{it}$  of the MOS capacitor decreases with increasing frequency. This result is reflected by the  $G_m/\omega/C_{ox}$  peak and frequency dispersion at depletion.  $R_s$  decreases with increasing frequency due to interface trapped charges, voltage-dependent fixed charges and mobile charges effect.

there is a hysteresis width due to electron and hole trapping in the interfacial layer [31].

The  $C_m/C_{ox}$ -V values have large frequency dispersion at the depletion region because of interface traps. The trapped charges at trap sites can easily follow the external ac signal because it is well known that the lifetime of interface trapped charges is lower than  $1/(\omega = 2\pi f)$ . Thus, interface trapped charges can affect the device's capacitance measurement. However, the trapped charges at trap sites cannot follow the external ac signal because the lifetime of interfacial trapped charges is much longer than  $1/(\omega = 2\pi f)$  of the ac signal at high frequencies (≥500 kHz) [29]–[33]. Therefore, interface trapped charges do not affect the device's capacitance measurement. The  $G_m/\omega/C_{ox}-V$  values have peaks for each frequency in the depletion region due to the exchange of low quantities of majority carriers in between the localized interface states and relevant band [29]-[33]. The magnitude of the peaks increased with decreasing frequency and shifted toward a lower voltage because of interface traps. This peak height can be directly attributed to  $D_{it}$ .

There are several methods to obtain the interface trap density  $D_{it}$ . The low-high frequency method is the most widely used method, but it is useful only if the density of interface traps is higher than  $10^{10} \text{ eV}^{-1}\text{cm}^{-2}$  [29], [30], [32], [33]. Another method to obtain interface traps is the conductance method. It is considered the most sensitive method [29], [30], [32], [33]. In addition, interface traps can be identified by using the Hill–Coleman method [16]

$$D_{\rm it} = \frac{2}{qA} \frac{G_{\rm mmax}/\omega}{\left[ \left( \frac{G_{\rm mmax}}{\omega} / C_{\rm ox} \right)^2 + (1 - C_m / C_{\rm ox})^2 \right]}$$

(1)

where A,  $\omega$ ,  $G_{\text{mmax}}$ ,  $C_m$ , and  $C_{\text{ox}}$  are the area of the device, angular frequency, maximum measured conductance value, capacitance value, and oxide capacitance of the device (or capacitance in the strong accumulation region), respectively. As can be seen in Fig. 5, the  $D_{\text{it}}$  of the MOS capacitor decreases with increasing frequency. This result is reflected by the  $G_m/\omega/C_{\text{ox}}$  peak and frequency dispersion at depletion in Fig. 4.

Another important electrical parameter, the series resistance  $(R_s)$  value, also has a large effect on the  $C_m G_m$ -V measurements and must be considered in the calculations.  $R_s$ has the potential to seriously affect admittance measurements. In order to prevent this as well as limitations on sensitivity,  $R_s$  should be minimized during fabrication of the sample. Alternatively, when measuring series resistance a correction factor should be applied to the measured C and  $G/\omega$  before the information is extracted [29], [30].

The series resistance of the diode was calculated by using following equation:

$$R_{s} = \frac{G_{m}(V)}{G_{m}^{2}(V) + (\omega C_{m}(V))^{2}}(2)$$

(2)

where  $C_m$  and  $G_m$  are the measured capacitance and conductance values and  $\omega$  is the angular frequency (= $2\pi f$ ) [33], [34]. Thus, the corrected capacitance ( $C_c$ ) and corrected equivalent parallel conductance ( $G_c$ ) equivalent frequency of interest are

$$C_c = \frac{\left[G_m^2 + (\omega C_m)^2\right]C_m}{\alpha^2 + (\omega C_m)^2}$$

(2a)

and

$$G_c = \frac{\left[G_m^2 + (\omega C_m)^2\right]\alpha}{\alpha^2 + (\omega C_m)^2}$$

(2b)

respectively, where  $\alpha = G_m - [(G_m)^2 + (\omega C_m)^2]R_s$  and  $C_m$  and  $G_m$  are the capacitance and the equivalent parallel conductance measured across the terminals of the MOS capacitor.

The causes of  $R_s$  are varied but include contact made by a probe to the gate or back contact of the semiconductor, the existence of impurities or dislocations in the material, high resistance in the quasi-neutral region in the bulk of the semiconductor and a nonuniform dopant concentration [29], [30], [35], [36]. As shown in Fig. 5,  $R_s$  decreases with increasing frequency. The frequency dependence of series resistance is the result of interface trapped charges, voltage-dependent fixed charges, and mobile charges [29], [30], [34], [36].

The  $C_m$  and  $G_m/\omega$  were corrected in order to eliminate the effect of  $R_s$ . The corrected capacitance  $(C_c)$  and conductance  $(G_c/\omega)$  are a function of the voltage at 1 MHz for the MOS capacitor [30]. Since the corrections were done on the capacitance and conductance values for the effect of  $R_s$ , while the values of  $C_c$  are higher than  $C_m$ , especially in the deplation and accumulation region, the corrected  $G_c/\omega$  values are lower than the  $G_m/\omega$  values.

As shown in Fig. 6(a) and (b),  $R_s$  is more effective in the depletion and accumulation region. However, it is easy to see that there is no significant error in the inversion region due to  $C_c$  being small (e.g.,  $(\omega R_s C_c)^2 \ll 1)$ .

#### C. Dielectric Properties

Dielectric parameters of the Ni/Au/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/p-Si MOS capacitor,  $\varepsilon'$  and  $\varepsilon''$  are described by the following equations

Fig. 6. Measured and corrected values of (a)  $C_m$  and  $C_c$ -V and (b)  $G_m$  and  $G_c/\omega$ -V of Ni/Au/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/p-Si MOS capacitor at 1 MHz.  $R_s$  is more effective in the depletion and accumulation region, although there is no significant error in the inversion region due to  $C_c$  being small [e.g.,  $(\omega R_s C_c)^2 \ll 1$ ].

[1]–[4]:

$$\varepsilon' = \frac{C_m}{C_o} \tag{3}$$

$$\varepsilon'' = \frac{G_m/\omega}{C_o}.$$

(4)

Here,  $C_o$  is the capacitance of free space ( $C_o = \varepsilon_o A/d_i$ ). A,  $\varepsilon_o$ , and  $d_i$  are the rectifier contact area, the permittivity of free space charge, and interfacial Ga<sub>2</sub>O<sub>3</sub> thin film thickness, respectively. The loss tangent can be defined using the following equation [5], [6]:

$$\tan \delta = \frac{\varepsilon''}{\varepsilon'}.$$

(5)

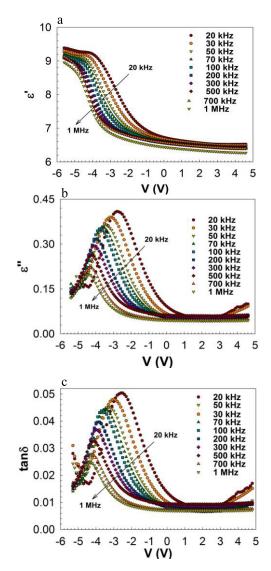

As seen in Fig. 7 (a)–(c), the  $\varepsilon'$ ,  $\varepsilon''$ , and  $\tan \delta$  are depend on frequency and voltage in the depletion region. The  $\varepsilon'$ values have a frequency distribution in the depletion region. On the other hand, the  $\varepsilon''$  and  $\tan \delta$  have peaks for each frequency and the peak position shifts toward lower voltages with decreasing frequency. Conversely, the magnitude of the peaks decreases with increasing frequency due to interface traps [29], [33]. There are several parameters which affect  $\varepsilon'$  $\varepsilon''$  and tan $\delta$ , such as  $D_{it}$ ,  $R_s$ , the thickness of the oxide layer and interfacial polarization [29], [33], [34], [37]. It is well known that interface traps can easily follow the ac signal at low frequencies, but at high frequencies, they cannot follow the ac signal due to the interface trap charge lifetime. Thus, dipolar and interfacial polarization types can contribute to  $\varepsilon'$ and  $\varepsilon''$  values at low frequencies. This dispersion can also be attributed to Maxwell-Wagner type interfacial polarization [38], [39]. As seen in Fig. 7(a), the value of  $\varepsilon'$  decreased with increasing frequency for each voltage at the depletion

Fig. 7. Voltage and frequency dependence (a) dielectric constant ( $\varepsilon'$ ) values have a frequency distribution in the depletion region due to interface traps. (b) Dielectric loss ( $\varepsilon''$ ) and (c) loss tangent (tan $\delta$ ) of Ni/Au/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/p-Si MOS capacitor have peaks and the magnitude of the peaks decreases with increasing frequency due to interface traps.

region. The interfacial and dipolar polarizations do not have enough time to orient themselves in the direction of the electric field. Therefore, dipolar and interfacial polarization become ineffective in the depletion region as the frequency increases [40]–[42].

Dielectric properties provide a great deal of information about thin films. However, it is difficult to see the dielectric relaxation peak in transition metal oxides due to the conduction current dominating the dielectric loss current. On the other hand, even without a clear dielectric relaxation peak, it is still possible to acquire information about the relaxation mechanism by looking at the dielectric modulus representation, which is the reciprocal of the dielectric permittivity [43]– [45]. M' and M'' are defined as follows:

$$M^* = M' + iM'' = \frac{\varepsilon'}{(\varepsilon')^2 + (\varepsilon'')^2} + i\frac{\varepsilon''}{(\varepsilon')^2 + (\varepsilon'')^2}.$$

(6)

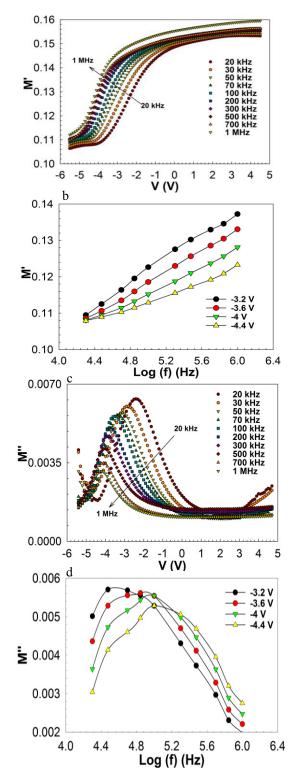

Fig. 8. Voltage and frequency dependence (a) real electrical modulus (M') values have dispersion in the depletion region and (b) M' values decreased with increasing frequency for each voltage due to relaxation process. (c) Imaginary electrical modulus (M'') values have a peak for each frequency in the depletion region and (d) also M'' versus log (f) also has a peak for each voltage.

As can be seen in Fig. 8(a), the M' values have dispersion in the depletion region and increase with increasing frequency for each voltage due to the relaxation process [Fig. 8(b)]. At lower frequencies, the value of M' is close to zero, which shows that electronic polarization does not occur. The M'' values have a

peak for each frequency in the depletion region [Fig. 8(c)]. And as seen in Fig. 8(d), M'' versus log (f) has a peak for each voltage. The angular frequency ( $\omega = 2\pi f$ ) at which the peak for M'' occurs can be determined using the equation  $\omega \tau = 1$ , where  $\tau$  is the relaxation time for a given angular frequency. Related results can be seen in the literature [43], [45]–[47].

## **IV. CONCLUSION**

In this paper, we have grown  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin film on p-type Si using the sol-gel method. The films were characterized using X-ray diffraction, and a detailed study of the electrical and dielectric properties were also performed. The experimental peak positions and intensities correspond well to a nearly randomly oriented monoclinic phase ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>). The electrical parameters of the diode such as breakdown field, interface trap density, and series resistance were obtained. The interface trap density was found to be  $10^{12} \text{ eV}^{-1} \text{cm}^{-2}$  using the Hill-Coleman method. This result is valuable for MOS capacitor applications. Dielectric parameters of the Ni/Au/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/p-Si MOS capacitor were investigated in the wide frequency range (20 kHz-1 MHz) at room temperature. We observed that these parameters have a strong dependence on frequency and voltage. This is especially true in the depletion region. All these factors demonstrate the interesting characteristics of solgel assisted  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin film which could be implemented as a good gate dielectric in MOSFETs.

#### REFERENCES

- X. Tan *et al.*, "Excellent-performance AlGaN/GaN fin-MOSHEMTs with self-aligned Al<sub>2</sub>O<sub>3</sub> gate dielectric," *Chin. Phys. Lett.*, vol. 33, no. 9, p. 098501, Sep. 2016.

- [2] D. Q. Xiao *et al.*, "Modification of optical and electrical properties of sol-gel-derived TiO<sub>2</sub>-doped ZrO<sub>2</sub> gate dielectrics by annealing temperature," *J. Alloys Compounds*, vol. 688, pp. 252–259, Dec. 2016.

- [3] A. Saeidi, A. Biswas, and A. M. Ionescu, "Modeling and simulation of low power ferroelectric non-volatile memory tunnel field effect transistors using silicon-doped hafnium oxide as gate dielectric," *Solid-State Electron.*, vol. 124, pp. 16–23, Oct. 2016.

- [4] C. Besleaga, G. E. Stan, I. Pintilie, P. Barquinha, E. Fortunato, and R. Martins, "Transparent field-effect transistors based on AlN-gate dielectric and IGZO-channel semiconductor," *Appl. Surf. Sci.*, vol. 379, pp. 270–276, Aug. 2016.

- [5] Z. Gao, M. F. Romero, M. A. Pampillon, E. San Andres, and F. Calle, "Thermal assessment of AlGaN/GaN MOS-HEMTs on Si substrate using Gd<sub>2</sub>O<sub>3</sub> as gate dielectric," *IEEE Trans. Electron Devices*, vol. 63, no. 7, pp. 2729–2734, Jul. 2016.

- [6] M. Passlack *et al.*, "Dielectric properties of electron-beam deposited Ga<sub>2</sub>O<sub>3</sub> films," *Appl. Phys. Lett.*, vol. 64, no. 20, pp. 2715–2717, May 1994.

- [7] J. Robertson, "High dielectric constant oxides," *Eur. Phys. J. Appl. Phys.*, vol. 28, pp. 265–291, Dec. 2004.

- [8] H. Y. Shih, F. C. Chu, A. Das, C. Y. Lee, M. J. Chen, and R. M. Lin, "Atomic layer deposition of gallium oxide films as gate dielectrics in AlGaN/GaN metal-oxide-semiconductor high-electron-mobility transistors," *Nanosc. Res. Lett.*, vol. 11, pp. 1–9, Apr. 2016.

- [9] W. Jevasuwan *et al.*, "Self-limiting growth of ultrathin Ga<sub>2</sub>O<sub>3</sub> for the passivation of Al<sub>2</sub>O<sub>3</sub>/InGaAs interfaces," *Appl. Phys. Exp.*, vol. 7, no. 1, p. 011201, Jan. 2014.

- [10] T. G. Allen, Y. Wan, and A. Cuevas, "Silicon surface passivation by gallium oxide capped with silicon Nitride," *IEEE J. Photovolt.*, vol. 6, no. 4, pp. 900–905, Jul. 2016.

- [11] O. Seok, W. Ahn, M. K. Han, and M. W. Ha, "Effect of Ga<sub>2</sub>O<sub>3</sub> sputtering power on breakdown voltage of AlGaN/GaN high-electron-mobility transistors," *J. Vac. Sci. Technol. B*, vol. 31, no. 1, p. 011203, Jan. 2013.

- [12] C. F. Lin, C. M. Lin, and R. H. Jiang, "Micro-square-array InGaNbased light-emitting diode with an insulated Ga<sub>2</sub>O<sub>3</sub> Layer through a photoelectrochemical process," *Jpn. J. Appl. Phys.*, vol. 51, no. 1, p. 01AG03, Jan. 2012.

- [13] K. Ulman, M. T. Nguyen, N. Seriani, and R. Gebauer, "Passivation of surface states of α-Fe<sub>2</sub>O<sub>3</sub>(0001) surface by deposition of Ga<sub>2</sub>O<sub>3</sub> overlayers: A density functional theory study," *J. Chem. Phys.*, vol. 144, no. 9, p. 094701, Mar. 2016.

- [14] A. Kumar, S. Mondal, and K. S. R. K. Rao, "Critical investigation of high performance spin-coated high-κ titania thin films based MOS capacitor," *J. Mater. Sci.-Mater. Electron.*, vol. 27, no. 5, pp. 5264–5270, May 2016.

- [15] M. H. Amiri, N. Namdar, A. Mashayekhi, F. Ghasemi, Z. Sanaee, and S. Mohajerzadeh, "Flexible micro supercapacitors based on laser-scribed graphene/ZnO nanocomposite," *J. Nanoparticle Res.*, vol. 18, no. 8, p. 237, Aug. 2016.

- [16] W. A. Hill and C. C. Coleman, "A single-frequency approximation for interface-state density determination," *Solid-State Electron.*, vol. 23, pp. 987–993, Sep. 1980.

- [17] Y. Alifragis, G. Roussos, A. K. Pantazis, G. Konstantinidis, and N. Chaniotakis, "Free-standing gallium nitride membrane-based sensor for the impedimetric detection of alcohols," *J. Appl. Phys.*, vol. 119, no. 7, p. 074502, Feb. 2016.

- [18] V. Lazarescu, M. Enache, M. Anastasescu, G. Dobrescu, C. Negrila, and M. F. Lazarescu, "Electrochemical impedance spectroscopy investigations on the L-cysteine-thiolate self-assembled monolayers formed at p-GaAs(100) electrodes," *Electrochim. Acta*, vol. 131, pp. 42–51, Jun. 2014.

- [19] Y. Cheng *et al.*, "Influence of N<sub>2</sub> and O<sub>2</sub> annealing treatment on the optical bandgap of polycrystalline Ga<sub>2</sub>O<sub>3</sub>:Cu films," *Mater. Sci. Semicond. Process.*, vol. 16, no. 5, pp. 1303–1307, Oct. 2013.

- [20] R. Suzuki, S. Nakagomi, Y. Kokubun, N. Arai, and S. Ohira, "Enhancement of responsivity in solar-blind β-Ga<sub>2</sub>O<sub>3</sub> photodiodes with a Au Schottky contact fabricated on single crystal substrates by annealing," *Appl. Phys. Lett.*, vol. 94, no. 22, p. 085102, Jun. 2009.

- [21] A. Goyal, B. S. Yadav, O. P. Thakur, A. K. Kapoor, and R. Muralidharan, "Effect of annealing on beta-Ga<sub>2</sub>O<sub>3</sub> film grown by pulsed laser deposition technique," *J. Alloys Compounds*, vol. 583, pp. 214–219, Jan. 2014.

- [22] V. Berbenni, C. Milanese, G. Bruni, and A. Marini, "Thermal decomposition of gallium nitrate hydrate Ga(NO<sub>3</sub>)<sub>3</sub>×xH<sub>2</sub>O," *J. Thermal Anal. Calorimetry*, vol. 82, no. 2, pp. 401–407, Nov. 2005.

- [23] Y. Zhou *et al.*, "Formation, etching and electrical characterization of a thermally grown gallium oxide on the Ga-face of a bulk GaN substrate," *Solid-State Electron.*, vol. 52, no. 5, pp. 756–764, May 2008.

- [24] L. M. Lin, Y. Luo, P. T. Lai, and K. M. Lau, "Influence of oxidation and annealing temperatures on quality of Ga<sub>2</sub>O<sub>3</sub> film grown on GaN," *Thin Solid Films*, vol. 515, no. 4, pp. 2111–2115, Dec. 2006.

- [25] H. Kim, S. J. Park, and H. S. Hwang, "Thermally oxidized GaN film for use as gate insulators," *J. Vac. Sci. Technol. B*, vol. 19, no. 2, pp. 579–581, Mar./Apr. 2001.

- [26] M. Passlack et al., "Ga<sub>2</sub>o<sub>3</sub> films for electronic and optoelectronic applications," J. Appl. Phys., vol. 77, no. 2, pp. 686–693, Jan. 1995.

- [27] H. Altuntus, I. Dönmez, Ç. Özgit, and N. Biyikli, "Effect of postdeposition annealing on the electrical properties of beta-Ga<sub>2</sub>O<sub>3</sub> thin films grown on p-Si by plasma-enhanced atomic layer deposition," *J. Vac. Sci. Technol. A*, vol. 32, no. 4, pp. 190–195, Jul. 2014.

- [28] A. Chin, B. C. Lin, W. J. Chen, Y. B. Lin, and C. Tsai, "The effect of native oxide on thin gate oxide integrity," *IEEE Electron Device Lett.*, vol. 19, no. 11, pp. 426–428, Nov. 1998.

- [29] S. M. Sze, "Citation classic—Physics of semiconductor-devices," Current Contents/Eng. Technol. Appl. Sci., no. 27, p. 28, 1982.

- [30] B. G. Streetman, "MOS (metal-oxide semiconductor) physics and technology," *Amer. Sci.*, vol. 71, no. 5, p. 549, 1983.

- [31] A. Turut, A. Karabulut, K. Ejderha, and N. Biyikli, "Capacitanceconductance-current-voltage characteristics of atomic layer deposited Au/Ti/Al<sub>2</sub>O<sub>3</sub>/n-GaAs MIS structures," *Mater. Sci. Semicond. Process.*, vol. 39, pp. 400–407, Nov. 2015.

- [32] A. Kaya *et al.*, "Ga<sub>2</sub>O<sub>3</sub> as both gate dielectric and surface passivation via sol-gel method at room ambient," *Proc. SPIE*, vol. 9957, pp. 9-99570–995709-8, Sep. 2016.

- [33] S. Altindal, Y. S. Asar, A. Kaya, and Z. Sonmez, "Investigation of interface states in Al/SiO<sub>2</sub>/p-Si (MIS) structures with 50 and 826 angstrom SiO<sub>2</sub> interfacial layer using admittance spectroscopy method," *J. Optoelectron. Adv. Mater.*, vol. 14, nos. 11–12, pp. 998–1004, Nov./Dec. 2012.

- [34] A. Kaya, S. Alialy, S. Demirezen, M. Balbaşı, S. A. Yerişkin, and A. Aytimur, "The investigation of dielectric properties and AC conductivity of Au/GO-doped PrBaCoO nanoceramic/n-Si capacitors using impedance spectroscopy method," *Ceram. Int.*, vol. 42, pp. 3322–3329, Feb. 2016.

- [35] K. Iniewski, A. Balasinski, B. Majkusiak, R. B. Beck, and A. Jakubowski, "Series resistance in a MOS capacitor with a thin gate oxide," *Solid-State Electron.*, vol. 32, no. 2, pp. 137–140, Feb. 1989.

- [36] K. J. Yang and C. Hu, "MOS capacitance measurements for highleakage thin dielectrics," *IEEE Trans. Electron Devices*, vol. 46, no. 7, pp. 1500–1501, Jul. 1999.

- [37] O. Bidault, P. Goux, M. Kchikech, M. Belkaoumi, and M. Maglione, "Space-charge relaxation in perovskites," *Phys. Rev. B, Condens. Matter*, vol. 49, no. 12, pp. 7868–7873, Mar. 1994.

- [38] J. C. Maxwell, A Treatise on Electricity and Magnetism, Unabridged, 3rd ed. New York, NY, USA: Oxford Univ. Press, 1998.

- [39] K. W. Wagner, "Zur theorie der unvollkommenen dielektrika," Annalen der Physik, vol. 345, no. 5, pp. 817–855, 1913.

- [40] A. Chełkowski, *Dielectric Physics* (Studies in Physical and Theoretical Chemistry). New York, NY, USA: Elsevier, 1980, p. 396.

- [41] E. H. Rhoderick, *Metal-Semiconductor contacts*. Oxford, U.K.: Clarendon Press, 1978.

- [42] P. Lunkenheimer, S. Krohns, S. Riegg, S. G. Ebbinghaus, A. Reller, and A. Loidl, "Colossal dielectric constants in transition-metal oxides," *Eur. Phys. J.-Special Topics*, vol. 180, pp. 61–89, Jan. 2010.

- [43] M. G. Hutchins, O. Abu-Alkhair, M. M. El-Nahass, and K. Abdel-Hady, "Electrical conductivity and dielectric relaxation in non-crystalline films of tungsten trioxide," *J. Non-Cryst. Solids*, vol. 353, nos. 44–46, pp. 4137–4142, Nov. 2007.

- [44] C. T. Moynihan, L. P. Boesch, and N. L. Laberge, "Decay function for electric-field relaxation in-vitreous ionic conductors," *Phys. Chem. Glasses*, vol. 14, no. 6, pp. 122–125, 1973.

- [45] C. T. Moynihan, "Description and analysis of electrical relaxation data for ionically conducting glasses and melts," *Solid State Ionics*, vol. 105, nos. 1–4, pp. 175–183, Jan. 1998.

- [46] T. Badapanda, S. Sarangi, S. Parida, B. Behera, B. Ojha, and S. Anwar, "Frequency and temperature dependence dielectric study of strontium modified barium zirconium titanate ceramics obtained by mechanochemical synthesis," *J. Mater. Sci.-Mater. Electron.*, vol. 26, no. 5, pp. 3069–3082, May 2015.

- [47] A. M. Mogus-Milankovic, A. Santic, V. Licina, and D. E. Day, "Dielectric behavior and impedance spectroscopy of bismuth iron phosphate glasses," *J. Non-Cryst. Solids*, vol. 351, nos. 40–42, pp. 3235–3245, Oct. 2005.

Jianyi Gao received the B.S. degree in electrical engineering from the Harbin Institute of Technology, Harbin, China, in 2011, and the M.S. degree from the Department of Electrical and Computer Engineering, University of Florida, Gainesville, FL, USA, in 2014. He is currently pursuing the Ph.D. degree with the School of Electrical, Computer and Energy Engineering, University of California, Davis, CA, USA, under the guidance of Dr. Chowdhury.

**Rajesh V. Chopdekar** received the M.S. and Ph.D. degrees in applied physics from Cornell University, Ithaca, NY, USA.

He is currently a Lecturer and a Research Associate with the University of California, Davis, CA, USA, where he is involved in exploring thin film magnetism in epitaxial complex oxide nanostructures and multilayers.

Yayoi Takamura received the B.S. degree in materials science and engineering from Cornell University, Ithaca, NY, USA, and the M.S. and Ph.D. degrees in materials science and engineering from Stanford University, Stanford, CA, USA. She is currently an Associate Professor with the University of California, Davis, CA, USA.

Ahmet Kaya received the M.S. and Ph.D. degrees in physics from Gazi University, Ankara, Turkey, in 2010 and 2013, respectively.

He is currently a Post-Doctoral Associate in the Integrated Nanodevices & Nanosystems (INANO) Lab of Prof. M. Saif Islam, University of California, Davis, CA, USA.

Srabanti Chowdhury (S'08–M'11) received the B.Tech. degree in radio physics and electronics from the Institute of Radio physics, Calcutta, India, in 2003, and the M.S and Ph.D. degrees in electrical engineering from the University of California, Santa Barbara, CA, USA, in 2008 and 2010.

She is currently an Assistant Professor with the University of California, Davis, CA, USA.

Howard Mao received the B.S. degree in electrical engineering from the University of California, Berkeley, CA, USA. He is currently pursuing the M.S. degree with the School of Electrical, Computer and Energy Engineering, University of California, Davis, CA, USA, under the guidance of Dr. M. Saif Islam.

**M. Saif Islam** received the B.Sc. (Hons.) degree in physics from Middle East Technical University, Ankara, Turkey, in 1994, and the M.S. and Ph.D. degrees in electrical engineering from the University of California, Los Angeles, CA, USA, in 1999 and 2001, respectively.

He is currently a Professor with the University of California, Davis, CA, USA.