Research

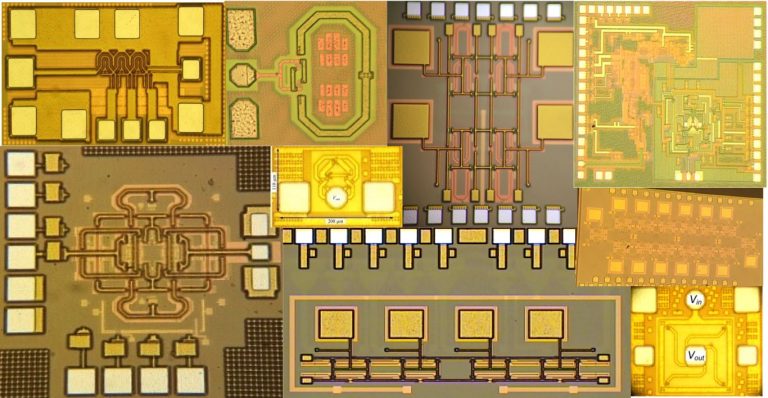

High-Speed Integrated Electronic Systems Lab (HISIES)

Our research is primarily focused on high-speed integrated circuits and systems. More specifically we are currently working on three important areas:

1) Study of theoretical limits of noise, power gain, harmonic generation, and output power of active and passive elements:

Our main approach to boost performance is to understand the detailed operation of devices at high frequencies and find different ways to push the performance of the device to its maximum theoretical limit. For example:

- We analyzed power-gain boosting and derived the exact component values to reach the theoretical gain limit of any transistor. [JSSC paper]

- We studied the underlying principle of harmonic generation and offered an intuitive way to understand and boost harmonic power at mm-wave and terahertz (THz) frequencies. [TMTT paper]

2) mm-wave and THz high-power and wide-band signal generation, radiation, and amplification:

Using the insight acquired from the theoretical analysis, we invent new circuit architectures to employ optimized devices. Broadly speaking, the main innovation here is the introduction of a systematic methodology for designing circuits operating at the limits of the transistors in any given process. This is achieved by blending device physics, circuit theory, and high frequency circuit design into a coherent technique. Below are some of the components that was implemented in silicon:

- A record 260 GHz amplifier [JSSC paper, ISSCC paper],

- A 190.5GHz mode-switching VCO with record 20.7% continuous tuning range [JSSC paper, ISSCC paper],

- A 0.34-THz varactor-less standing wave radiator array with 5.9% tuning range [RFIC paper],

- A 52-142GHz band-pass distributed amplifier with average gain of 14.4dB,

- A highly efficient 0.2 THz varactor-less VCO [TMTT paper, CSICS paper].

3) Integrated system architectures for mm-wave and THz applications:

Not too long ago, envisioning a CMOS terahertz system-on-chip did not seem realistic. To achieve an ultimate goal of high performance systems, optimum system architectures should be combined with transistor level components. Here we work on different aspects of high frequency system architecture to make it efficient for mm-wave and terahertz operation. Examples are:

- A 318-to-370GHz standing-wave 2D phased array with record tuning range [ISSCC paper],

- A 300GHz frequency synthesizer with record 7.9% locking range [JSSC paper, ISSC paper],

- Low noise and high conversion gain THz receiver array,

- Extremely low power mm-wave frequency synthesizer,

- High data rate wireless links.